MÉTODO DE FABRICACIÓN DE ESTRUCTURAS DE PUERTA DE TRANSISTORES MOSFET SOBRE SEMICONDUCTORES III-V

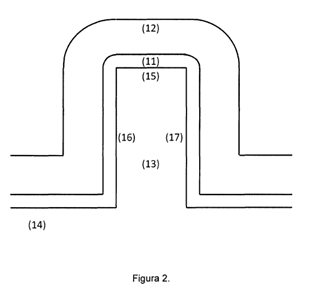

Sección perpendicular al flujo de electrones dentro de un dispositivo FinFET

RESUMEN

Esta invención propone aplicar la pulverización de alta presión de nanoláminas metálicas de escandio y un lantánido y su posterior oxidación por plasma temperatura ambiente sobre sustratos semiconductores III-V, de interés para dispositivos MOSFET, tanto planares como FinFETs. La ventaja de estos semiconductores es que tienen mayor movilidad de portadores en el canal que el Si, mayor transconductancia y menor retardo de conmutación con respecto a la tecnología actual.

Se obtienen estructuras MOS funcionales sobre semiconductores alternativos al Si con un óptimo recubrimiento de escalones. Solamente se necesitan tecnologías de vacío alto-medio y que tienen un menor impacto medioambiental que sus alternativas. Supone una simplificación del proceso de fabricación al no tener que realizarse ningún proceso de depuración-filtrado-limpieza de residuos muy dañinos para el medio ambiente y reducción de los tiempos de vacío previo al depósito.

SECTOR DE LA TÉCNICA

Esta invención se encuadra de la fabricación de dispositivos semiconductores, dentro del sector de la microelectrónica.

INVENTORES

María Ángela Pampillón Arce

Carmina Cañadilla Soto

Pedro Feijoo Guerro

Enrique San Andrés

Álvaro Del Prado Millán

María Luisa Lucía Mulas